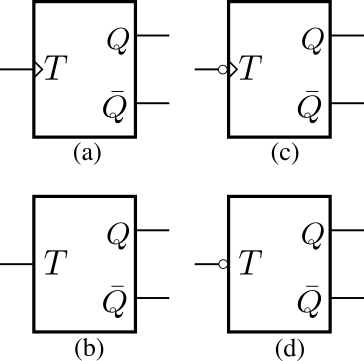

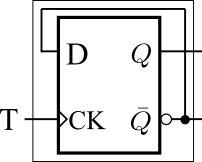

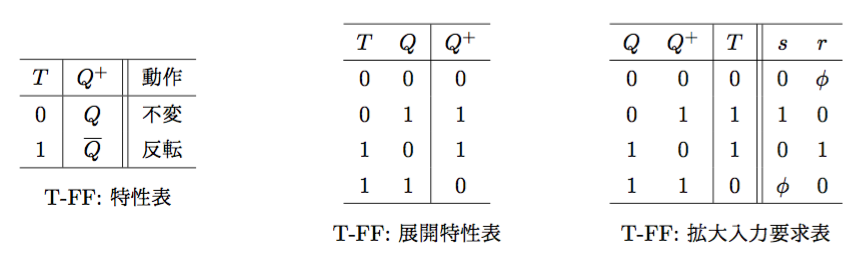

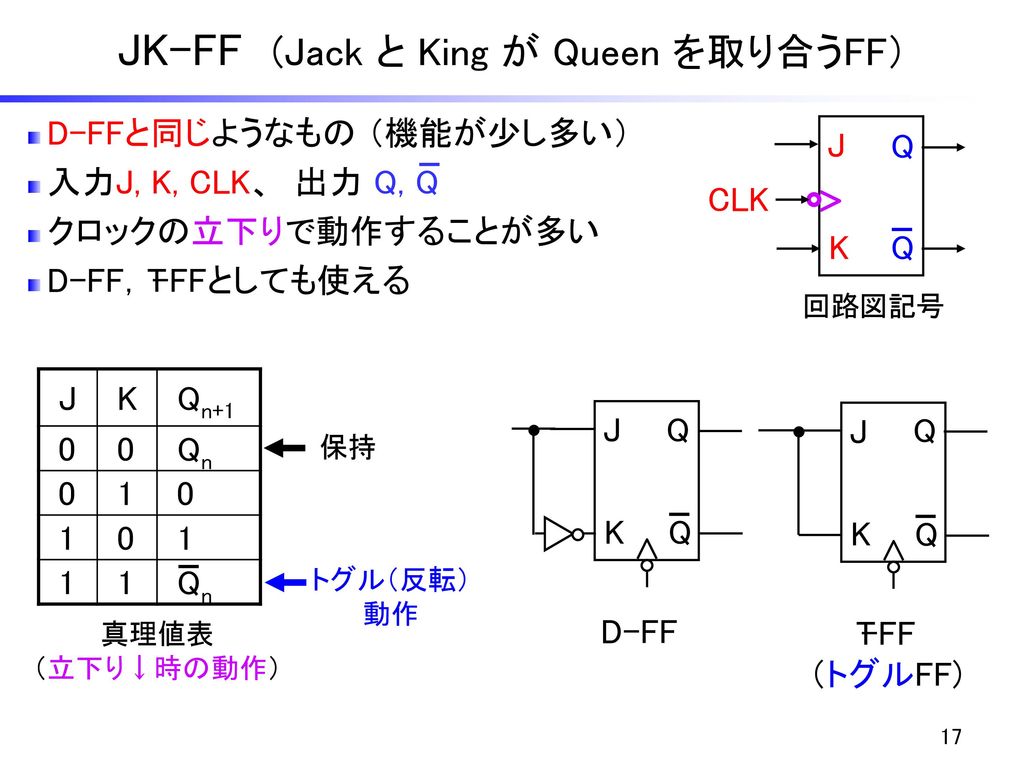

この回路図、何か変です。 一般にtffの入力はtだけでこれがクロック入力になります。提示図のようにtとckがあるffは見たことがありません。(似たものでdとckを持つffはある) 出題者はたぶん「tが'1'の時のckの立上りでqが変化 (2) jp a 10 30May 22, 08 · 電子回路ドリル II(18) MONOist 問題16 DFFでカウンタを作る : 完全マスター! 電子回路ドリル II(18) » 08年05月22日 00時00分 公開Oct 11, 19 · 以下の図は、各端子における入力されたパルス信号と出力されたパルス信号です。 各端子における入力されたパルス信号と出力されたパルス信号 Q1 と Q2 から出力されるパルス信号にて電圧が低いを0、電圧が高いを1とすると、回路の真理値表は以下の

Tフリップフロップの真理値表や回路図を分かりやすく簡単に解説 なんとなくわかる 大学の数学 物理 情報

T-ff 回路図

T-ff 回路図-組み合わせ回路(combinational logic) 順序回路 (sequential logic) 順序回路: フリップフロップ 真理値表 (動作表) → 簡単化 → 回路図 TFF × 2 出力 𝑄 𝑛 (1)(clr回路なし,jkff3段)2/2 回路構成 ffa 出力qとffbのck 接続 ja に接続 ka=jb=kb=kc=1 (vcc) and 入力 ,出力jc ckffa,ffcに接続 強制clrのない5進カウンタである qc qa,qb q j q k >ck clr ck vcc(1) qa q j q k >ck clr qb clr ffa ffb q j q k >ck clr qc ffc 論理回路 摂大・鹿間 tffによる

フリップフロップ

Q f r L P > K g d > M > q > M > j c b > M > h r _ e > ` n q u b > n l X r > > > > > > S t > > Lきる同期式順序回路が多く用いられている。 5 考察 この実験を通して、同期式カウンタの設計法と同期式tff,dff,jkff の動作の特徴および利用法を学ぶことができた。 6 感想 実験は回路が入り組んで分かりにくかったが、どうにかミスをせずに完成パラメータ Number of channels (#) 2 Technology Family CD4000 Supply voltage (Min) (V) 3 Supply voltage (Max) (V) 18 Input type Standard CMOS Output type PushPull Clock Frequency (Max) (MHz) 24 IOL (Max) (mA) 68 IOH (Max) (mA)68 ICC (Max) (uA) 600 Features Balanced outputs, Standard speed (tpd > 50ns), Positive input clamp diode openinnew その他の D タイプ・フリッ

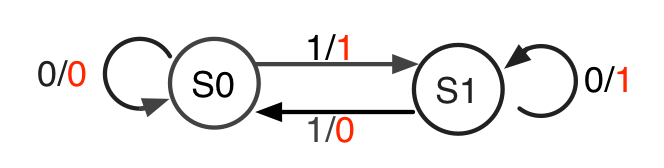

00/8/7,11「vlsi設計・夏の学校」 ディジタル回路設計の基礎 4 同期回路とは? 時間方向を同期パルス(クロック)により、量子化 (ディジタル化)した回路 クロックにより、クロックとの間のタイミングを考 慮するだけでよくなる。組み合わせ回路 この回路を ff 設計する 外部入力 i1, i2, , im 外部出力 o1, o2, , on 状態 q1, q2, , qk 同期式回路の設計 1 入力(i1, i2, im),出力(o1, o2, on),状 態(q1, q2, qk)を決める 2 状態遷移図を描く 3 状態遷移表を作成する 4 拡大入力要求表を作成する 5(a) 回路図 (b) タイミング図 論理回路基礎 東大・坂井 非同期アップダウンカウンタ 制御信号によって昇順・降順を変えられるカウンタ jkffの間は、2チャネルマルチプレクサの回路が入る コントロール端子: H=アップ、L=ダウン j q q k set clr

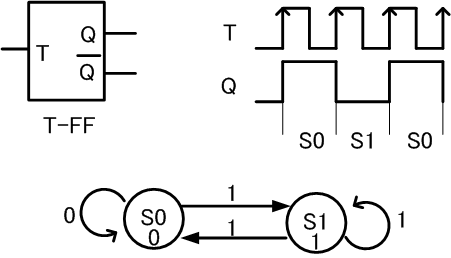

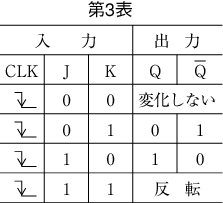

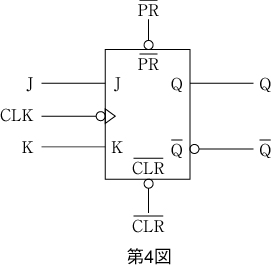

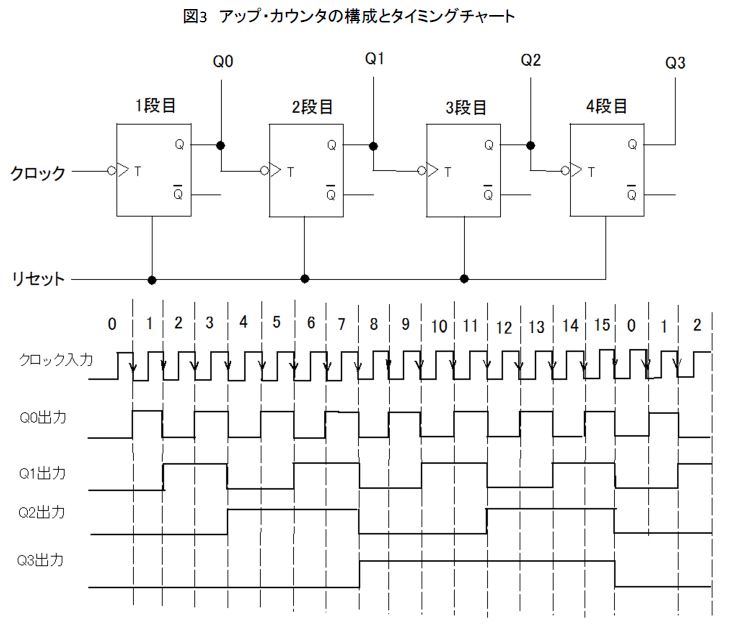

T ff は2 個の信号が入力されると元の状態に戻る回路である. タイミングチャート t q (ポジティブエッジトリガーの場合) 横軸を時間にし, 縦軸を各変数の 値としたグラフ これをn 個接続して2n 進カウンター (計数回路)を作ることができる. q cl t q1 t q2 t q3 ・・・・ q qOct 05, 12 · TFF回路(ラッチ回路) 下記のようなTFF回路をNAND回路4つ使用し、実際に組んでみたのですが、 正常に動作しません。 Cに1パルスを入力すると出力はHighで固定されますが、もう一度Cに1パルスを入力しても 出力はHighのままLowに変わりません。May 01, 08 · 電子回路ドリル II(16) MONOist 問題14 JKFFのタイムチャート : 完全マスター! 電子回路ドリル II(16) » 08年05月01日 00時00分 公開

状態遷移図 石丸技術士事務所 ディジタル技術資料

フリップフロップ

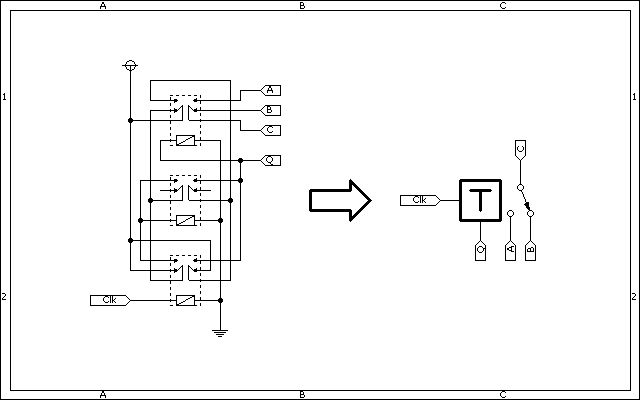

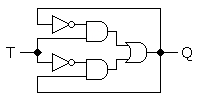

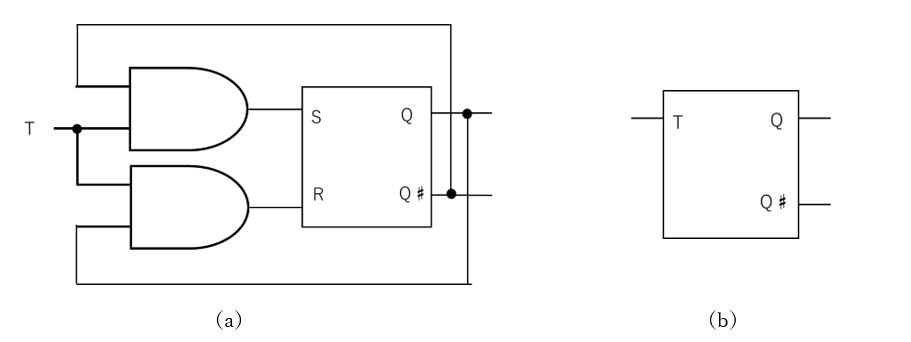

ゲート回路による tff の回路図 RSFF を用いて TFF を構成すると次に示す回路となる。 RSFF を用いて構成した TFF の回路図論理回路 摂大・鹿間 k j q q ck 0 遅延 遅延 ネガティブエッジトリガjkffの動作(sn74lvc112a) case #21:q 0,q 1(ck 0) ( 配線を省略)clr,pre 0 0 0 1 0 0 0 0 0 0 1 0 1 1 1 1 j, k 入力によらずリセット状態を保持 論理回路 摂大・鹿間 k j q q ck 0 遅延 遅延Jun 14, 21 · 問題 VirtualBoxを用いて、KaliをゲストOSとした仮想マシンを構築したとします。その際、Kaliを起動すると、ドラゴンのロゴが出たところで止まるという現象が報告されています。

フリップフロップとカウンタ 公益社団法人 日本電気技術者協会

フリップフロップ回路 Youtube

回路図の右の真理値表は回路図と連動して、行の背景色が黄色に変わります。 信号線の青は0、赤は1を表します。 デジタル回路入門3回目となる今回は、「順序回路」とその動作の要となるフリップフロップについて解説します。 前回学んだ「組み合わせ次式のDFFの特性方程式を用いて,順序回路を構成する. つまり,状態遷移図の「次の状態Y」をDFFのQ n1と考えれば良い 以上より,DFFの入力方程式は 4) 回路図 Q n1 =D Y=Q n1 DFF:入力Dが次の状態Q n1 入力方程式: FFの入力を現状態yと入力xで記述.この入力により33 tff の応用:分周器・・・1個のtffで周波数が1/2になる t q q t _ q q _ t q q _ t1 t2 t3 q1 q2 q3 p p q1 q2 q3 注)前段の変化が次々に影響が波及⇒直流駆動型、非同期式カウンタなど

デジタル回路設計入門

フリップフロップ Wikipedia

図2 本実験でのディジタル回路設計の流れ 本実験では、仕様設計(システムの特性や機能について検討する) と機能分割(どのようなハードウェ ア、ソフトウェアを使用するかを検討する) はすでに終わっているものとし、図2 のような流れで開発をAug 05, 15 · Tフリップフロップは、入力信号の制御で出力信号が反転 (トグル)するフリップフロップです。 図1は回路図でTフロップフロップを表すシンボルです。 入力端子としてT、出力端子として Q と Q ― を持ちます。 Q ― は Q の反転値が出力されます。下に tffを用いた2進カウンタ の 回路図 を示します。 なお、このTFFは第2章で紹介した パルス型(AC型) ではなく、 入力 T の立ち上り直後に出力 Q が反転する DC型のTFF であることに注意して

回路図修正 電気電子技術研究室 Eet Lab

01 号 分周回路 Astamuse

0 2 clr 5 進カウンタの回路図 5 個目のパルスが入力された直後に,q 2 q 1 q 0 の出力は二進数で5 を表す ので,この論理値の組み合わせで,3 入力nand 回路をアクティブ(l)にし,すべてのjkffT ff は2 個の信号が入力されると元の状態に戻る回路である. タイミングチャート t q (ポジティブエッジトリガーの場合) 横軸を時間にし, 縦軸を各変数の 値としたグラフ これをn 個接続して2n 進カウンター (計数回路)を作ることができる. q cl t q1 t q2 t q3 ・・・・ q q回路記号 特性表 タイミングチャート 図29 tff ff を順序回路の記憶回路部に用いる場合、ff の状態(出力)q が順序回路の状 態変数に対応する。次時刻に、状態変数を所望の値にする、すなわち、ff が所

Tフリップフロップの真理値表や回路図を分かりやすく簡単に解説 なんとなくわかる 大学の数学 物理 情報

Digital Circuit Lab4

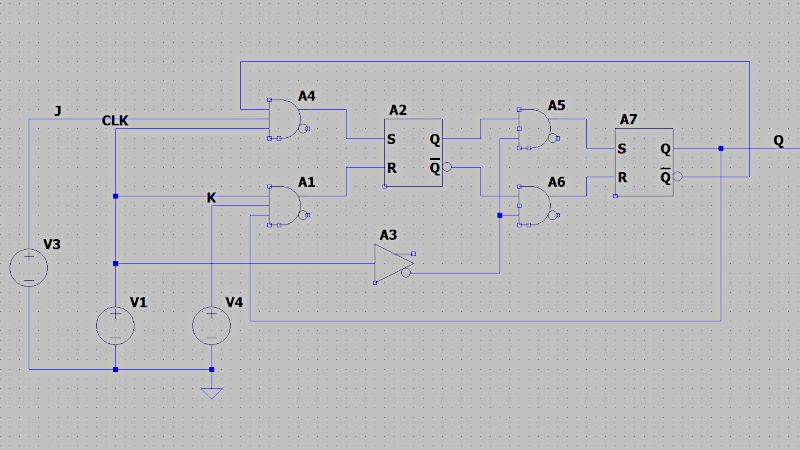

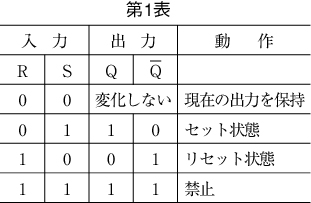

下図の基本論理ゲートで構成した回路(1)と シミュレータ内に登録されているjkフリップフロップ(2)が どちらも クロック信号(ck)に同期して教科書p66, 図107 に示してある動作をし, jkフリップフロップとして機能することを確認せよ.帰還を持つインバータ回路(2個の場合) 2つの安定状態を持つ インバータの個数と安定/発振の関係 奇数個の場合:発振 偶数個の場合:2つの安定状態を持つ hlhlhl( 1 ) ( ) s r q t q t s r q t rsffの回路構成(1-1) 2番目の式に ド・モルガンの 法則を適用 r s q q rsffは,norを使って以下の回路で与えることができる.

フリップフロップ Wikipedia

アップダウンカウンタの制作 基礎編 マルツセレクト

図1 Qucsのメインウィンドウ Qucsで出来るデジタルシミュレーションは、真理値表だけではありません。回路に任意の信号を印加し、タイミング図に出力信号を観測することもできます。回路構成は少し複雑 クロックはキャリーの伝播 遅延時間とffのスイッチング 遅延時間で決まる (非同期式より遅い) カウント値が安定する のに必要な時間が短い 出力にハザードが発生しない 用途 低速の回路 高い周波数のクロック の分周回路Mar 07, 21 · TFF フリップフロップ の一つ。 Tフリップフロップ、Tタイプ、あるいは「トグル」と呼ばれ、入力があるたびに保持内容が反転する。 バイナリカウンター や リップルカウンター は、このフリップフロップで作られる。

論理回路 フリップフロップの動作原理 Youtube

Chap10

Jun 18, 19 · 3回目の研修では順序回路の説明を行い、同期式5進カウンタを設計しました。組み合わせ回路は現在の入力値で出力が決まりますが、順序回路は 現在の内部状態=過去の入力の履歴で決まる論地回路です。あらかじめ定めた時間間隔ごとに状態が更新される同期式順序回路が主流になって6進カウンタ回路を tff を用いて作成するときの回路図を示しなさい。 入力中で3個連続した1を見つける回路を実現しなさい。 自動販売機の状態遷移図において、S1からの遷移 100/01 の表わす内容を説図2-2 に分周回路のブロック図を示す。 図2-2.分周回路のブロック図 1mhz のclk を、10 進カウンタで1/10 ずつ4 回分周し、4 段目の桁上げ出 力から100hz のパルスを得る。本設計では、10 進(bcd)カウンタとして 74hc160 を使用した。74hc160 のピン配置と真理値表

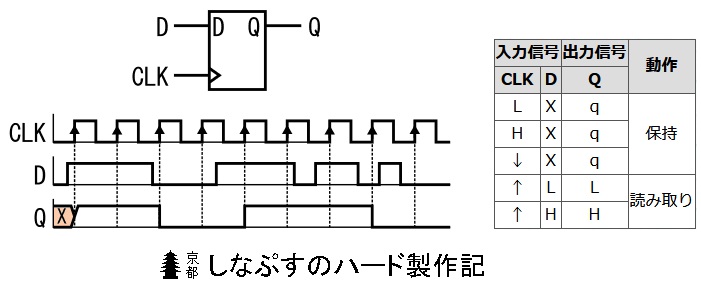

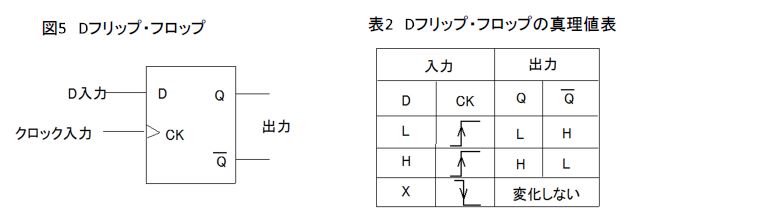

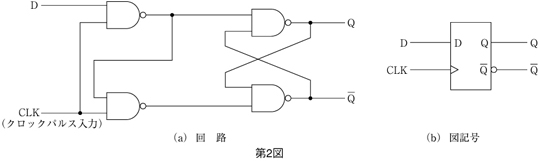

Dフリップフロップ の解説 1 しなぷすのハード製作記

Dフリップフロップ

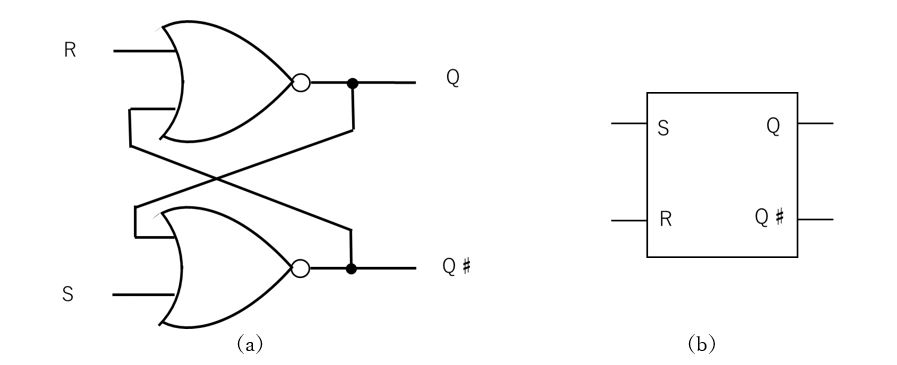

回路で、中央処理装置内部のレジスタやキャッシュメモリなど、記憶を司る回路に使用されてい ます。ここでは、構造が最もシンプルな図430 のRS フリップフロップ4について解説します5。 図中のS (Set) とR (Reset) は入力、Q とQ は出力を表します6。2 1 RS FF RSフリップフロップ回路は,図 1 に示すように, S (Set) , R (Reset) の二つの入力端子を持ち,この入力によって状態が決められ,その状態を 維持する. S に"1"が加えられるとQは"1" となり, R に"1"が加えられると Q は,"0"となる.そして出力の状態が決まった後は,入力を"0"にしても出力は変わ らず,そのまま保持される.これが2進1桁の記憶に相当する順序論理回路は内部状態と入力の組み合わせで出力が決まる。 これを記述するのに、状態遷移図を作成する。状態遷移図に基 づき指定された動作を行う順序論理回路を設計する。 2.順序論理回路 組み合わせ論理回路では 出力=f(入力)

フリップフロップとカウンタ 公益社団法人 日本電気技術者協会

フリップフロップ

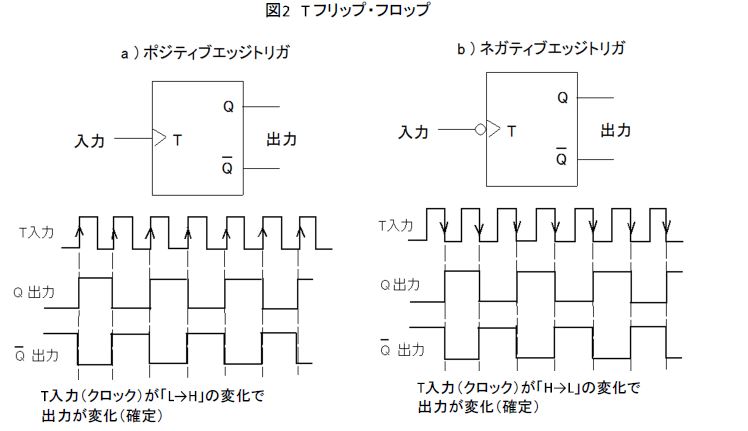

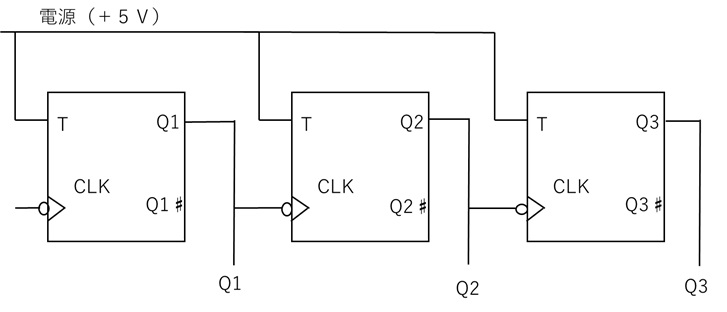

これより、上の中央の回路図が得られます。なお、この tff を簡略化した記号(図の下)で表すことがあります。 次に、この tff の タイムチャート を示します。 上の図で、入力信号 t = 1 の幅が狭いことに注意して下さい。Mar 05, 21 · 図2 t型フリップフロップ(カウンタ回路) 図2はtffの入力端子を電源に接続し、ハイレベルに固定したもので、clkパルスが2個入力されるたびにqとq♯に1個のパルスが出力される様子を示しています。(赤で示した部分) tffを直列に接続した回路 図3はtffを3個直列に接続した場合の回路構成で、図4はそのタイムチャートです。

Tフリップフロップ 石丸技術士事務所 ディジタル技術資料

Digital Circuit Lab4

真理値表 の解説 しなぷすのハード製作記

早わかり電子回路 カウンタ回路とは 前提となる2進数の理解から丁寧に解説 アイアール技術者教育研究所 製造業エンジニア 研究開発者のための研修 教育ソリューション

問題14 Jk Ffのタイムチャート 完全マスター 電子回路ドリル Ii 16 Monoist

フリップフロップ Wikipedia

問題14 Jk Ffのタイムチャート 完全マスター 電子回路ドリル Ii 16 Monoist

マスタスレーブtフリップフロップの問題を解いていたのですが だんだ 工学 教えて Goo

Computer Archtecture

5 フリップフロップ Digital Electronic Circuits 1 0 ドキュメント

アップダウンカウンタの制作 基礎編 マルツセレクト

2 原理

問題13 Sr Ffのタイムチャート 完全マスター 電子回路ドリル Ii 15 Monoist

フリップフロップ

5 フリップフロップ Digital Electronic Circuits 1 0 ドキュメント

Tff 通信用語の基礎知識

早わかり電子回路 順序回路とは フリップフロップの種類と同期の方法を学ぶ アイアール技術者教育研究所 製造業エンジニア 研究開発者のための研修 教育ソリューション

日本財団図書館 電子図書館 通信講習用 船舶電気装備技術講座 レーダー 基礎理論編

マイクラ Tフリップフロップの解説と作り方 隠しドアなどにも Youtube

アップダウンカウンタの制作 基礎編 マルツセレクト

フリップフロップ Wikipedia

フリップフロップ Wikipedia

T Flip Flop 回路 マイクラポケット辞典

フリップフロップ

宮崎技術研究所 の技術講座 電気と電子のお話 5 2 3 G

フリップフロップ

Tフリップフロップ 石丸技術士事務所 ディジタル技術資料

宮崎技術研究所 の技術講座 電気と電子のお話 5 2 3 G

Jk Ffを使用してt Ff D Ffを作成せよという問題で特性 Yahoo 知恵袋

トランジスタの見た夢 その2 トランジスタの見た夢

論理回路 Logic Circuit Kanetaiの二次記憶装置

日本財団図書館 電子図書館 通信講習用 船舶電気装備技術講座 gmdss 基礎理論編

フリップフロップ

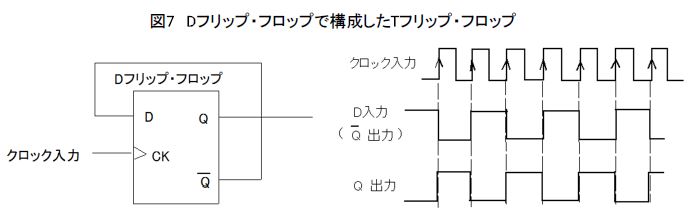

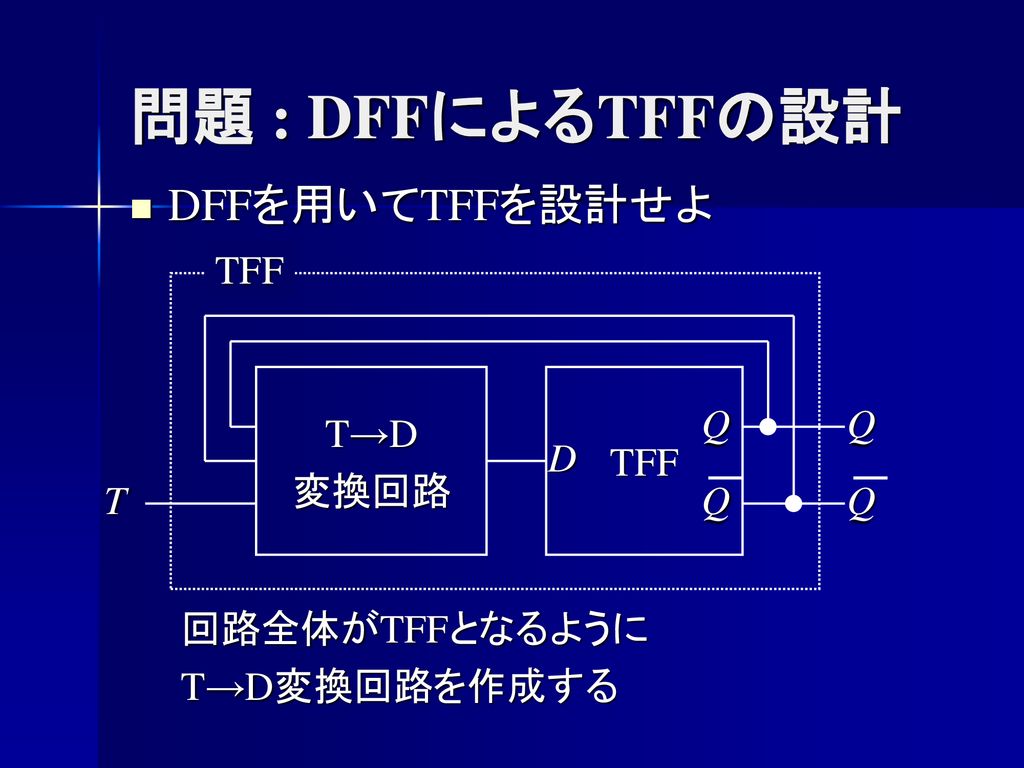

至急 論理回路の設計について T Ffをd Ffで設計せよ と Yahoo 知恵袋

Computer Archtecture

フリップフロップ

アップダウンカウンタの制作 基礎編 マルツセレクト

宮崎技術研究所 の技術講座 電気と電子のお話 5 2 3 G

論理回路 第9回 フリップフロップ 38号館4階n 411 内線 Ppt Download

フリップフロップ

フリップフロップとカウンタ 公益社団法人 日本電気技術者協会

Untitled Document

フリップフロップ

Tフリップフロップの意味 用法を知る Astamuse

Tフリップフロップの真理値表や回路図を分かりやすく簡単に解説 なんとなくわかる 大学の数学 物理 情報

フリップフロップ

Dフリップフロップ

Jkv Gog6gepigm

日本財団図書館 電子図書館 通信講習用 船舶電気装備技術講座 レーダー 基礎理論編

トランジスタの見た夢 その2 トランジスタの見た夢

早わかり電子回路 順序回路とは フリップフロップの種類と同期の方法を学ぶ アイアール技術者教育研究所 製造業エンジニア 研究開発者のための研修 教育ソリューション

情報画像学実験ii 実験1 論理回路

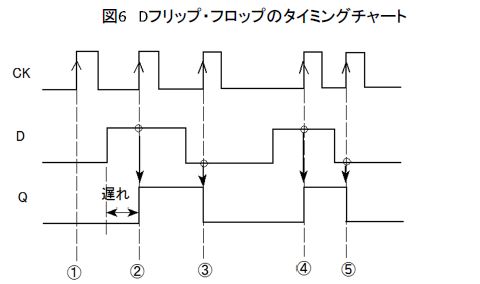

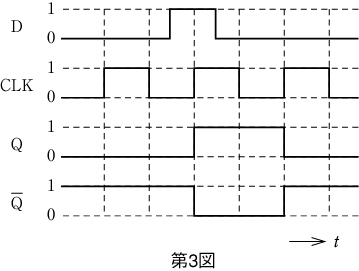

第10回 Dフリップフロップ ディジタル回路で特に重要な D Ff 仕組みを理解する タイミング図を読み書きできるようにする 瀬戸 Ppt Download

記憶素子 フリップフロップ

Basicプログラミング

フリップフロップとカウンタ 公益社団法人 日本電気技術者協会

Untitled Document

うさぎでもわかる計算機システム Part08 フリップフロップ D T Rs Jk クロックとタイミングチャートの書き方 工業大学生ももやまのうさぎ塾

フリップフロップ

Tフリップフロップの真理値表や回路図を分かりやすく簡単に解説 なんとなくわかる 大学の数学 物理 情報

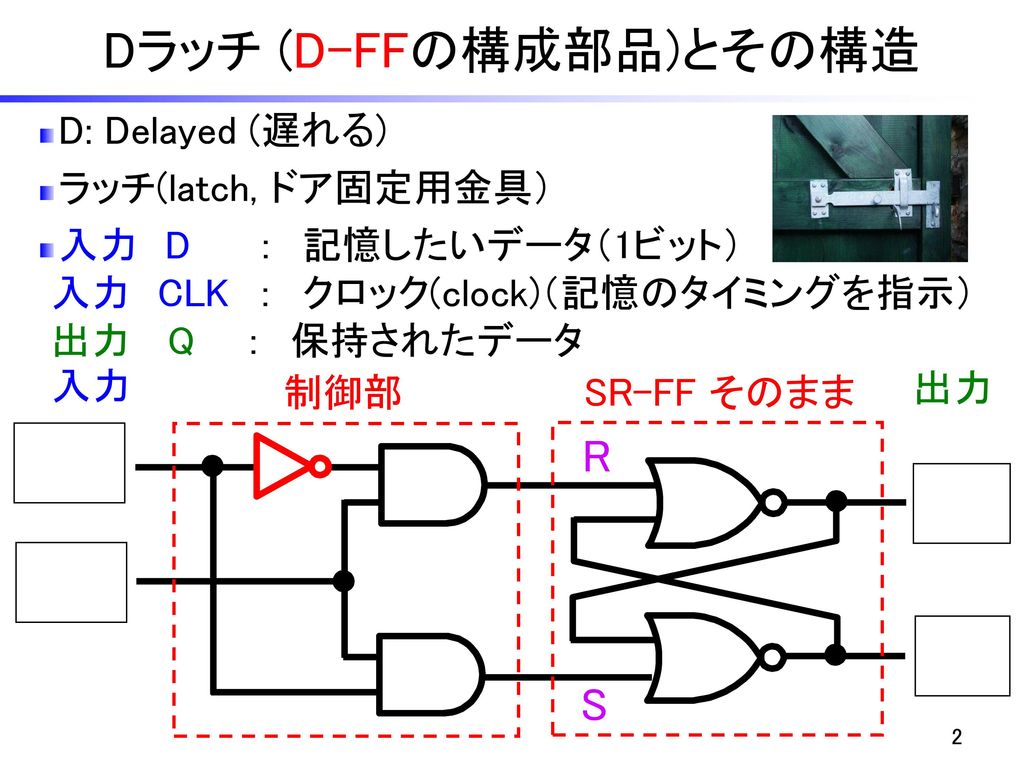

ラッチ回路 Wikipedia

ミーリ マシンの状態遷移図例 石丸技術士事務所 ディジタル技術資料

カウンタ

Tフリップフロップの真理値表や回路図を分かりやすく簡単に解説 なんとなくわかる 大学の数学 物理 情報

アップダウンカウンタの制作 基礎編 マルツセレクト

フリップフロップについて質問です Jk Ffでt Ffを作った Yahoo 知恵袋

5 フリップフロップ Digital Electronic Circuits 1 0 ドキュメント

フリップフロップとカウンタ 公益社団法人 日本電気技術者協会

Digital Circuit Lab4

第10回 Dフリップフロップ ディジタル回路で特に重要な D Ff 仕組みを理解する タイミング図を読み書きできるようにする 瀬戸 Ppt Download

Digital Circuit Lab4

5 フリップフロップ Digital Electronic Circuits 1 0 ドキュメント

フリップフロップ

フリップフロップ

5 フリップフロップ Digital Electronic Circuits 1 0 ドキュメント

もっとも簡単な10進カウンタを作る

カウンタとシフトレジスタ Cpuを作ろう 計算機教材とマイコンと電子工作 楽天ブログ

フリップフロップ

フリップフロップ

フリップフロップとカウンタ 公益社団法人 日本電気技術者協会

フリップフロップ

フリップフロップ

0 件のコメント:

コメントを投稿